在高速數(shù)字電路設(shè)計(jì)中��,時(shí)鐘信號(hào)如同系統(tǒng)的心跳���,任何微小的時(shí)序偏差都可能引發(fā)連鎖反應(yīng)。而時(shí)鐘緩沖器作為信號(hào)完整性的"守門人"���,其選型直接影響著系統(tǒng)穩(wěn)定性�、功耗表現(xiàn)和成本控制���。工程師常面臨這樣的困境:參數(shù)表上琳瑯滿目的指標(biāo)如何轉(zhuǎn)化為設(shè)計(jì)優(yōu)勢(shì)��?本文將拆解選型過(guò)程中的關(guān)鍵決策因子���,助您在復(fù)雜的應(yīng)用場(chǎng)景中快速鎖定最優(yōu)解。

一���、基礎(chǔ)參數(shù)決定選型基準(zhǔn)

1.1 輸入/輸出類型匹配度

時(shí)鐘緩沖器的接口必須與主時(shí)鐘源和負(fù)載端完全兼容�����。LVDS�、LVPECL�、HCSL等差分信號(hào)類型需嚴(yán)格對(duì)應(yīng),單端信號(hào)則需確認(rèn)電壓標(biāo)準(zhǔn)(如1.8V/2.5V/3.3V)�。例如,Xilinx UltraScale+ FPGA的參考時(shí)鐘若采用HCSL輸出����,配套緩沖器應(yīng)支持HCSL輸入轉(zhuǎn)LVDS輸出功能。

1.2 抖動(dòng)性能的量化評(píng)估

抖動(dòng)參數(shù)需分層解讀:

周期抖動(dòng)(Period Jitter):直接影響同步電路建立/保持時(shí)間余量

相位噪聲(Phase Noise):在射頻系統(tǒng)中決定頻譜純度

附加抖動(dòng)(Additive Jitter):緩沖器自身引入的噪聲應(yīng)小于系統(tǒng)總預(yù)算的10%

二�、應(yīng)用場(chǎng)景驅(qū)動(dòng)的差異化選型

2.1 通信設(shè)備:低抖動(dòng)優(yōu)先

在5G基站或光模塊中,時(shí)鐘信號(hào)需穿越多個(gè)時(shí)鐘域�。推薦使用集成PLL的智能緩沖器,支持輸入時(shí)鐘丟失自動(dòng)切換功能�����,確保系統(tǒng)在±50ppm頻偏下仍能維持鎖定��。

2.2 消費(fèi)電子:成本與功耗平衡

智能手表等設(shè)備需在靜態(tài)功耗<1μA與動(dòng)態(tài)響應(yīng)速度間取舍��。采用多電壓域設(shè)計(jì)的緩沖器可動(dòng)態(tài)關(guān)閉空閑通道����,實(shí)測(cè)數(shù)據(jù)顯示其功耗比傳統(tǒng)方案降低43%。

通過(guò)系統(tǒng)化評(píng)估時(shí)鐘緩沖器技術(shù)參數(shù)���、應(yīng)用場(chǎng)景�����,工程師可構(gòu)建完整的選型決策矩陣���。在具體實(shí)踐中���,建議使用參數(shù)權(quán)重評(píng)分法,對(duì)抖動(dòng)��、功耗�����、成本等指標(biāo)賦予差異化權(quán)重�����,通過(guò)量化分析找到最優(yōu)平衡點(diǎn)��。

時(shí)鐘系統(tǒng)

時(shí)鐘系統(tǒng)

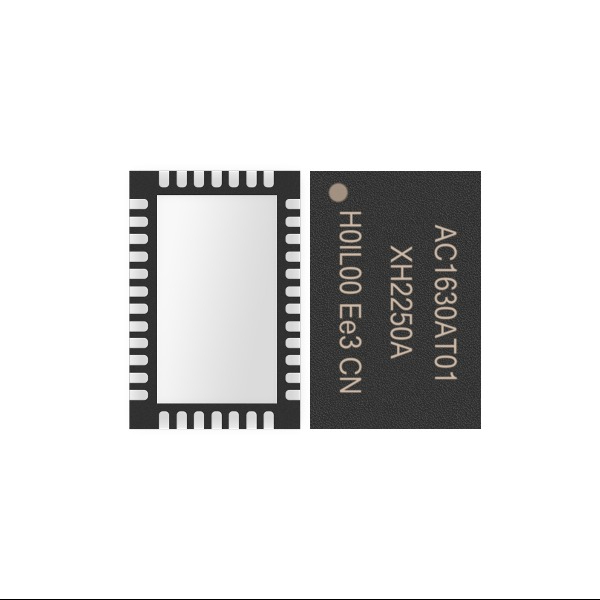

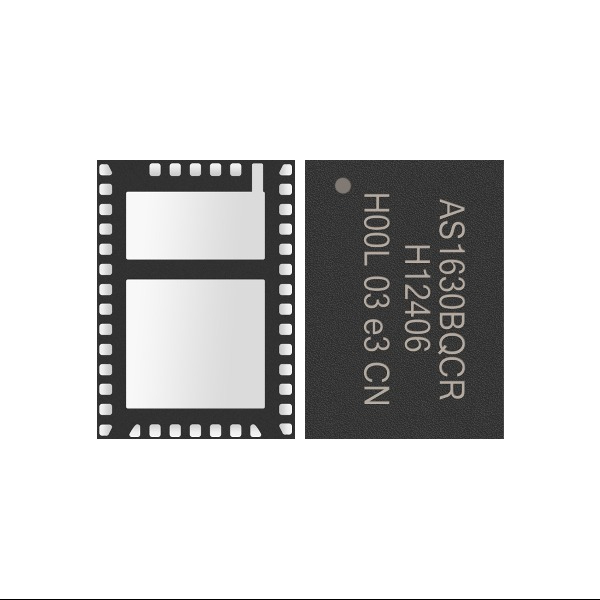

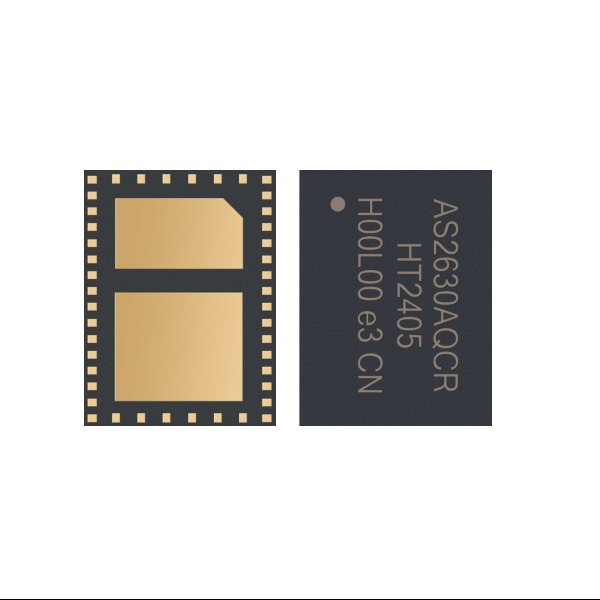

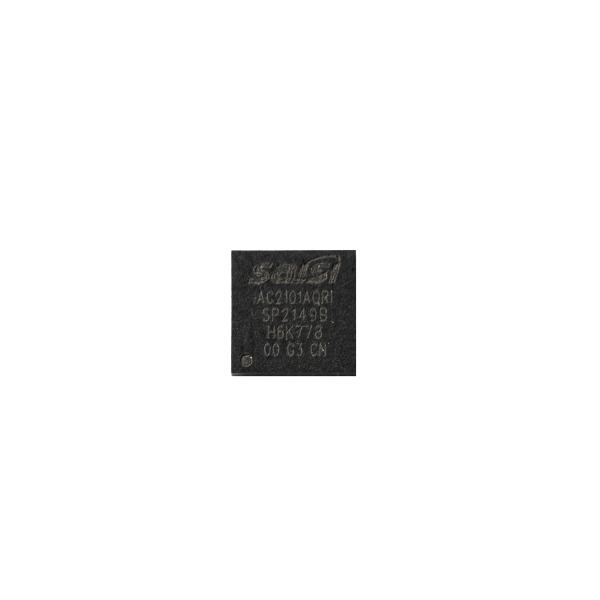

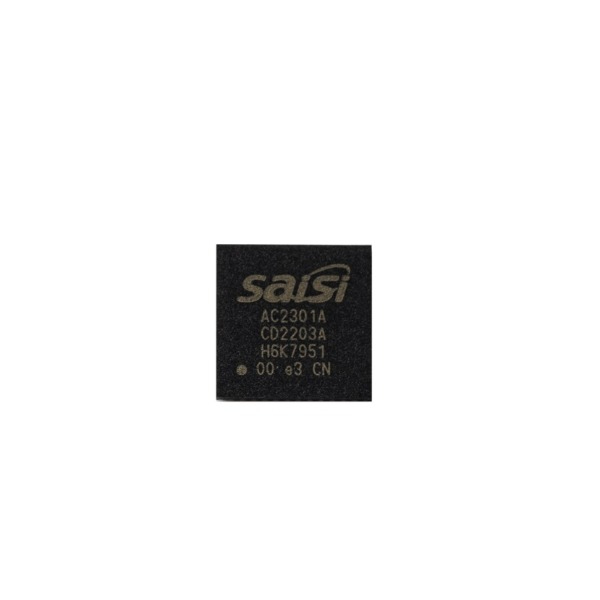

芯片

芯片

晶振&原子鐘

晶振&原子鐘

授時(shí)板卡

NTP時(shí)間同步服務(wù)器PTP時(shí)間同步服務(wù)器時(shí)間同步裝置授時(shí)安全防護(hù)裝置網(wǎng)同步設(shè)備/時(shí)頻一體化設(shè)備子母鐘系統(tǒng)BBU池時(shí)間同步時(shí)統(tǒng)設(shè)備鐘組設(shè)備測(cè)試儀器光纖雙向設(shè)備網(wǎng)管系統(tǒng)語(yǔ)音芯片時(shí)鐘發(fā)生器時(shí)鐘緩沖器時(shí)鐘SOC芯片晶振原子鐘授時(shí)模塊

授時(shí)板卡

NTP時(shí)間同步服務(wù)器PTP時(shí)間同步服務(wù)器時(shí)間同步裝置授時(shí)安全防護(hù)裝置網(wǎng)同步設(shè)備/時(shí)頻一體化設(shè)備子母鐘系統(tǒng)BBU池時(shí)間同步時(shí)統(tǒng)設(shè)備鐘組設(shè)備測(cè)試儀器光纖雙向設(shè)備網(wǎng)管系統(tǒng)語(yǔ)音芯片時(shí)鐘發(fā)生器時(shí)鐘緩沖器時(shí)鐘SOC芯片晶振原子鐘授時(shí)模塊 TS3000(4U)電力時(shí)間同步裝置

TS3000(4U)電力時(shí)間同步裝置 TS3000(1U)NTP時(shí)間服務(wù)器

TS3000(1U)NTP時(shí)間服務(wù)器 TS8000子母鐘系統(tǒng)

TS8000子母鐘系統(tǒng) TS3000模塊化NTP服務(wù)器

TS3000模塊化NTP服務(wù)器 SM2000時(shí)頻同步設(shè)備/網(wǎng)同步設(shè)備/bits設(shè)備

SM2000時(shí)頻同步設(shè)備/網(wǎng)同步設(shè)備/bits設(shè)備 NS7200(2U)萬(wàn)兆接口NTP服務(wù)器

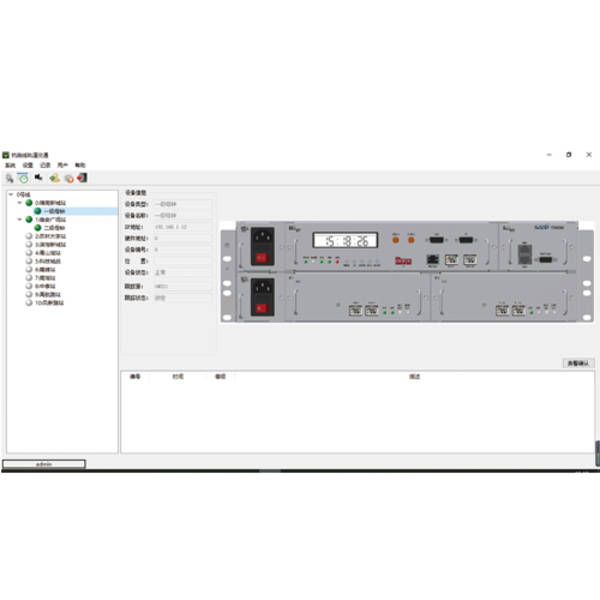

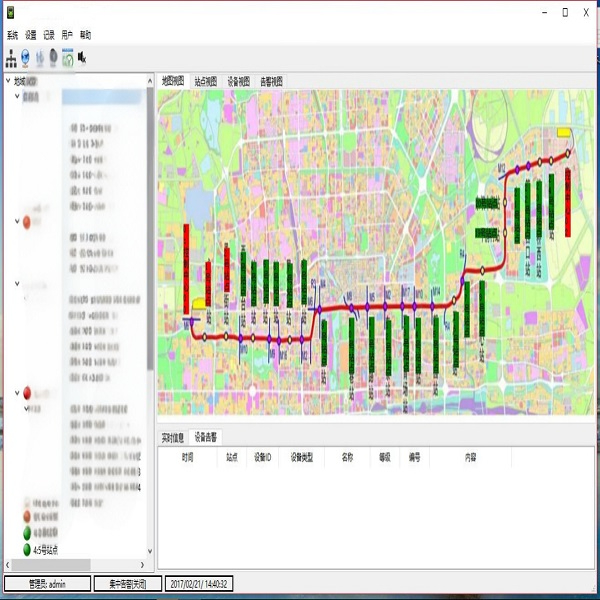

NS7200(2U)萬(wàn)兆接口NTP服務(wù)器 同步網(wǎng)綜合網(wǎng)管

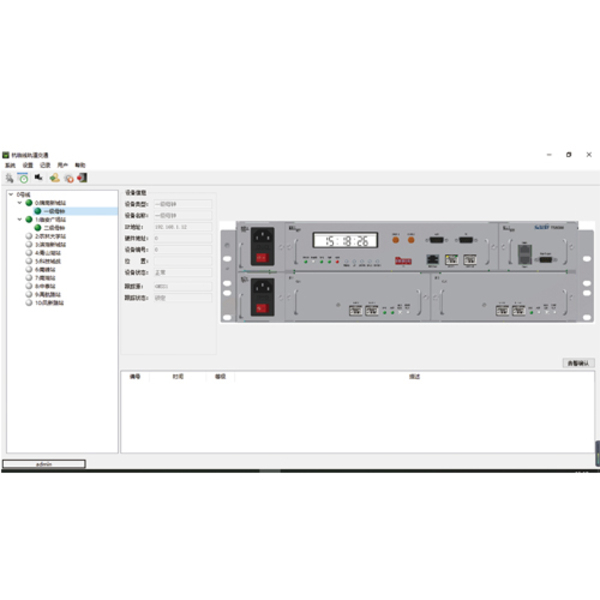

同步網(wǎng)綜合網(wǎng)管 /NTP/RS422TS8000擴(kuò)展箱

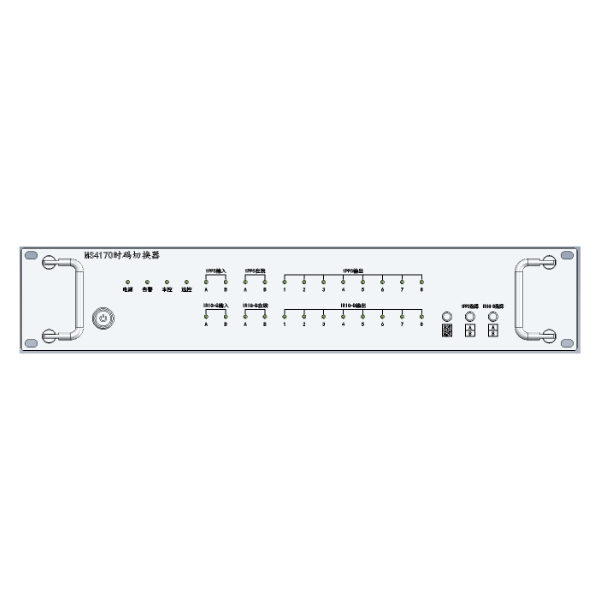

/NTP/RS422TS8000擴(kuò)展箱 MS4170時(shí)碼切換器

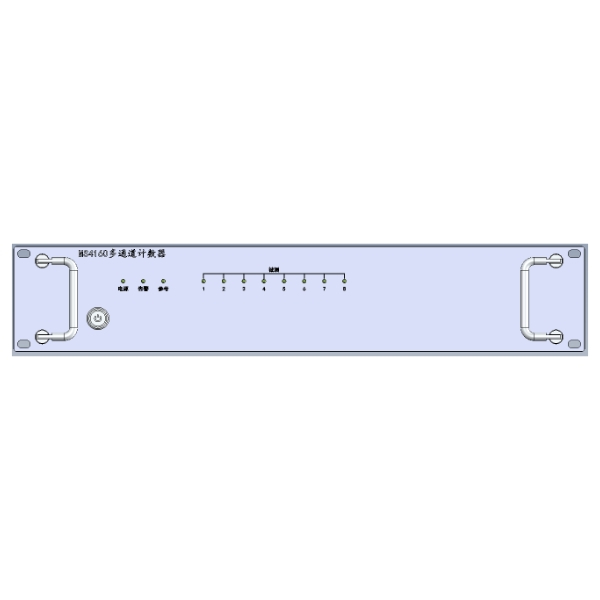

MS4170時(shí)碼切換器 MS4160多通道計(jì)數(shù)器

MS4160多通道計(jì)數(shù)器 MS4150時(shí)碼產(chǎn)生器

MS4150時(shí)碼產(chǎn)生器 MS4140北斗共視儀

MS4140北斗共視儀 MS4130相位微躍計(jì)

MS4130相位微躍計(jì) MS4110相位比對(duì)器

MS4110相位比對(duì)器

智能電網(wǎng)

智能電網(wǎng)

通信網(wǎng)絡(luò)

通信網(wǎng)絡(luò)

智慧交通

智慧交通

智能樓宇

智能樓宇

數(shù)據(jù)中心

數(shù)據(jù)中心

前沿領(lǐng)域

前沿領(lǐng)域

新聞資訊

新聞資訊

人才研學(xué)中心

人才研學(xué)中心

加入賽思

加入賽思

關(guān)于賽思

關(guān)于賽思