在現(xiàn)代高速數(shù)字系統(tǒng)中���,時鐘信號的完整性直接影響著系統(tǒng)的性能和穩(wěn)定性。時鐘緩沖器作為時鐘樹設(shè)計的核心組件�����,承擔(dān)著信號分配�����、噪聲隔離和時序優(yōu)化的關(guān)鍵任務(wù)��。隨著5G通信��、AI芯片和數(shù)據(jù)中心等領(lǐng)域的快速發(fā)展�,工程師在選型與設(shè)計時鐘緩沖器時,既要滿足多路低抖動輸出的需求����,又要應(yīng)對復(fù)雜電磁環(huán)境下的信號完整性問題�。本文將深入剖析時鐘緩沖器技術(shù)選型的核心指標(biāo)與設(shè)計中的隱性風(fēng)險點�,為工程師提供可落地的解決方案。

一�、技術(shù)選型的五大黃金準(zhǔn)則

1. 抖動性能:系統(tǒng)時序的生死線

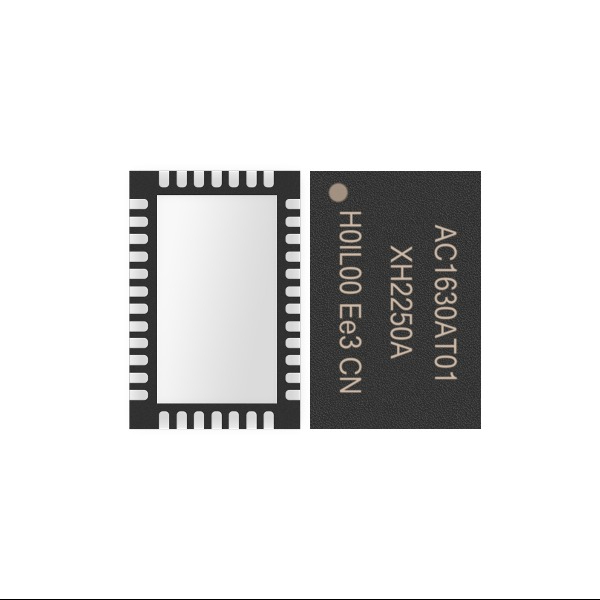

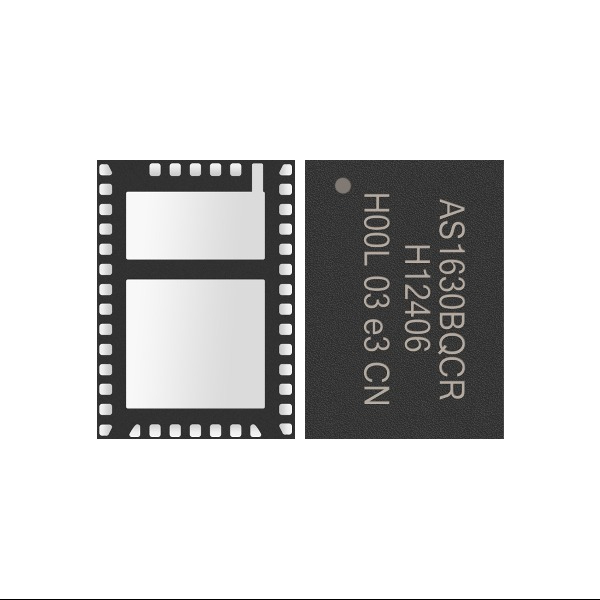

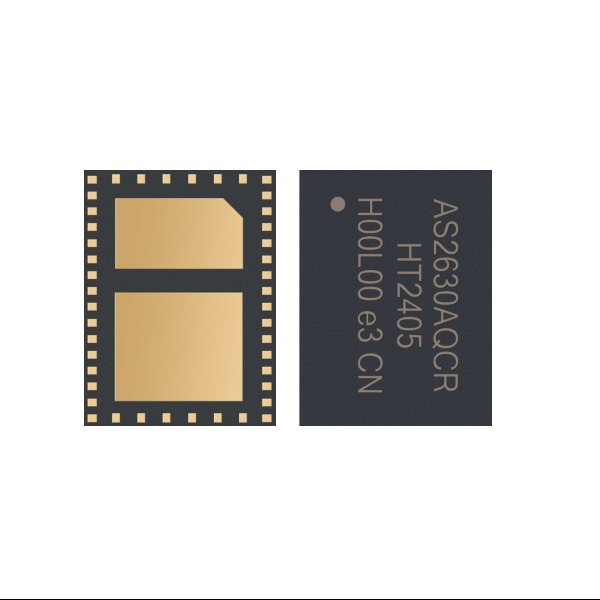

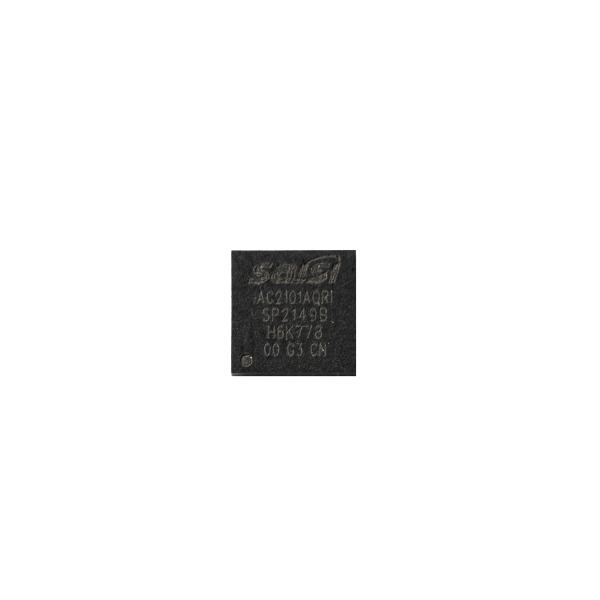

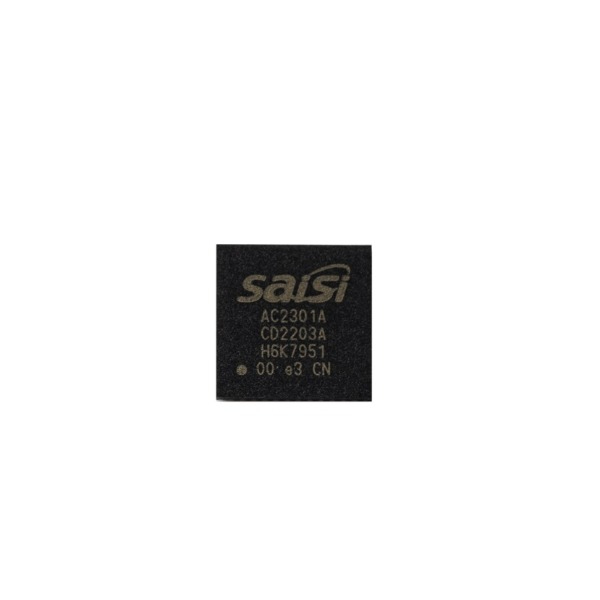

時鐘緩沖器的輸出抖動(Jitter)直接決定下游電路的時序余量。根據(jù)IEEE 1156標(biāo)準(zhǔn)�,RMS相位抖動應(yīng)低于300fs@156.25MHz才能滿足高速SerDes接口要求。例如�,賽思的AC系列通過混合信號PLL架構(gòu),在1.8V供電下實現(xiàn)<100fs的超低抖動���,特別適用于400G光模塊等場景。

2. 輸出通道數(shù)與靈活性

在多核處理器和FPGA系統(tǒng)中���,時鐘緩沖器的輸出通道數(shù)需匹配負(fù)載需求����。具有獨立使能控制的8通道器件相比固定分頻方案���,可動態(tài)配置不同頻率域��,降低系統(tǒng)功耗達(dá)30%�����。

3. 供電電壓與功耗的平衡術(shù)

在移動設(shè)備中�����,1.2V低電壓器件的靜態(tài)電流需控制在5mA以內(nèi)�。賽思的AC系列采用動態(tài)偏置技術(shù),在待機模式下功耗僅3μA���,同時支持1.5V至3.3V寬電壓輸入�,適配異構(gòu)計算平臺的混合供電架構(gòu)��。

4. 封裝熱阻與散熱設(shè)計

QFN-24封裝的熱阻(θJA)通常為35°C/W���,當(dāng)環(huán)境溫度超過85°C時���,需通過PCB散熱過孔矩陣將結(jié)溫控制在105°C以下。實測數(shù)據(jù)顯示�,增加4×4陣列的0.3mm散熱孔可使溫升降低18%。

5. 抗干擾能力的隱藏指標(biāo)

電源抑制比(PSRR)>60dB@100MHz的器件能有效隔離開關(guān)電源噪聲���。以賽思的AC系列為例���,其差分輸入結(jié)構(gòu)配合片上LDO����,可將電源噪聲引起的相位誤差減少至傳統(tǒng)方案的1/5�。

以上就是關(guān)于“時鐘緩沖器技術(shù)選型與設(shè)計要點”的相關(guān)內(nèi)容,希望能對您有所幫助�����。

時鐘系統(tǒng)

時鐘系統(tǒng)

芯片

芯片

晶振&原子鐘

晶振&原子鐘

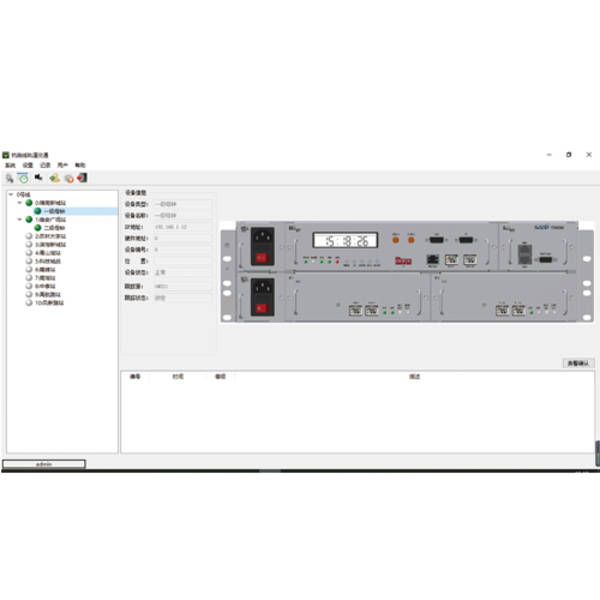

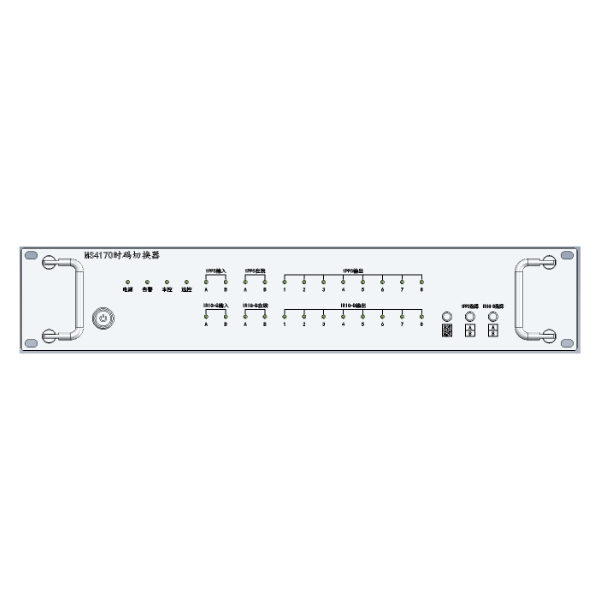

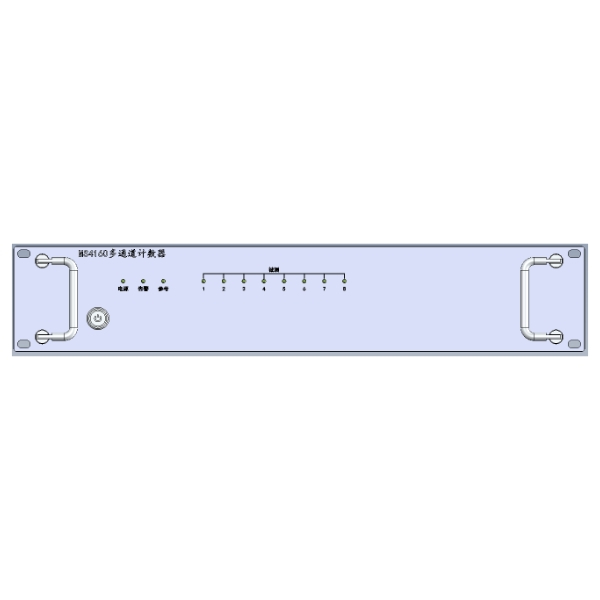

授時板卡

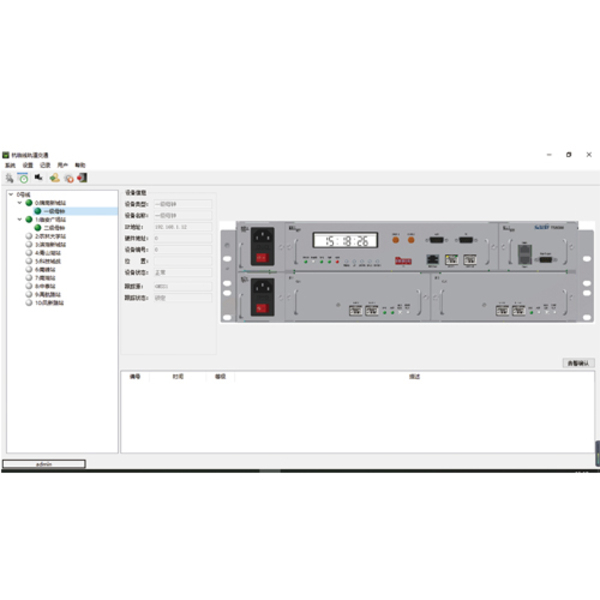

NTP時間同步服務(wù)器PTP時間同步服務(wù)器時間同步裝置授時安全防護(hù)裝置網(wǎng)同步設(shè)備/時頻一體化設(shè)備子母鐘系統(tǒng)BBU池時間同步時統(tǒng)設(shè)備鐘組設(shè)備測試儀器光纖雙向設(shè)備網(wǎng)管系統(tǒng)語音芯片時鐘發(fā)生器時鐘緩沖器時鐘SOC芯片晶振原子鐘授時模塊

授時板卡

NTP時間同步服務(wù)器PTP時間同步服務(wù)器時間同步裝置授時安全防護(hù)裝置網(wǎng)同步設(shè)備/時頻一體化設(shè)備子母鐘系統(tǒng)BBU池時間同步時統(tǒng)設(shè)備鐘組設(shè)備測試儀器光纖雙向設(shè)備網(wǎng)管系統(tǒng)語音芯片時鐘發(fā)生器時鐘緩沖器時鐘SOC芯片晶振原子鐘授時模塊

智能電網(wǎng)

智能電網(wǎng)

通信網(wǎng)絡(luò)

通信網(wǎng)絡(luò)

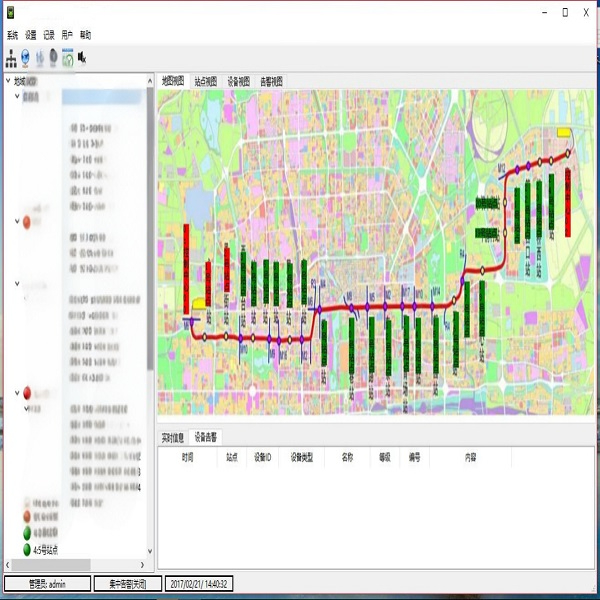

智慧交通

智慧交通

智能樓宇

智能樓宇

數(shù)據(jù)中心

數(shù)據(jù)中心

前沿領(lǐng)域

前沿領(lǐng)域

新聞資訊

新聞資訊

人才研學(xué)中心

人才研學(xué)中心

加入賽思

加入賽思

關(guān)于賽思

關(guān)于賽思